1. Внутренние прерывания микропроцессора.

В ранних МП системах например

система К 580 механизма внутренних прерываний вообще не было. В современных МП

предусмотрено несколько внутренних прерываний генерирующих при выполнение

программы. В частности команда INT h вызывает прерывание сразу после своего завершения.

Тип прерывания и определяет адрес вызываемой процедуры обслуживания прерывания.

Пример: 1)int 10h;прерывание

видеосистемы.

2)int 21h;прерывание функций О.С., работа с файловой

структурой, работа с данными.

Кроме того есть команда

внутренних прерываний INTO, которая

генерирует фиксированное прерывание с кодом 4 после своего завершения, если

установлен флажок 0F .

МП самостоятельно генерирует

прерывания типа 0 сразу после выполнения команд деления и целочисленного

деления (DIV и IDIV) если формат частного превышает формат получателя ошибка деления.

Если флажок TF установлен в 1 то МП автоматически генерирует

прерывание с кодом типа 1 после выполнения каждой команды.

Внутренние прерывания

характеризуются следующими свойствами:

1.

Тип прерывания

либо предопределен, либо содержится в коде команды.

2.

Цикл шины INTA не формируется.

3.

Внутренние

прерывания нельзя запрещать кроме прерывания пошаговой работы.

4.

Любое внутреннее

прерывание за исключением (прерывания пошаговой работы) имеет более высокий

приоритет чем внешние прерывания.

2. Таблица указателей векторов прерываний.

Таблица указателей векторов

прерываний осуществляет связь между кодом типа прерывания и процедурой которая

обслуживает прерывания данного типа. Таблица занимает 1кБ памяти в диапазоне

адреса от 0 до 3FFh и может содержать до 256

элементов, каждый i-й элемент этой таблицы представляет собой полный (2

слова) начальный логический адрес. Процедуры которые обслуживают прерывания

типа i слово с

большим адресом содержит базовый адрес сегмента, а слово с меньшим адресом

содержит смещение процедуры от начала сегмента.

Каждый элемент

таблицы состоит из 4-х байт и МП вычисляет адрес нужного элемента путем

простого умножения кода типа прерывания на 4 (двойной сдвиг в лево).

Первые 128 байт

данных таблицы зарезервированы для фиксированных типов прерываний, их нельзя

использовать для других целей.

Перед вызовом

процедуры обслуживания прерываний и включение в стек содержимого регистра

флагов МП инициирует процедуру прерывания выполняя действия:

Эквивалентные действию

команды межсегментного косвенного вызова CALL. Адресом передачи управлении при этом служит полный

адрес содержащийся в найденном элементе таблицы.

Переход через таблицы

указателей.

Код типа прерывания

В

большинстве систем основной объём памяти реализован на микросхемах DRAM. Однако для повышения быстродействия в ПК

используется высокоскоростная кэш-память. Обычно она построена на технологии SRAM (Static

random access memory). В отличие от DRAM технология SRAM не

требует постоянного обновления содержимого. Кроме того, контроллер памяти может

считывать содержимое памяти без его разрушения. Поэтому время доступа к МС SRAM составляет 10нс и меньше. В МС SRAM для хранения 1-го бита информации не используются

конденсатор, заряд которого необходимо обновлять, но используется несколько

транзисторов (5-6), поэтому МС SRAM обладает

меньшей ёмкостью, чем МС DRAM такого же

размера. Высокое быстродействие понижает ёмкость и повышает цену. Высокая цена

делает МС SRAM более пригодной для

реализации кэш-памяти, а не ОЗУ.

Рассмотрим

различия между статической и динамической памятью.

В статической памяти ячейки

построены на различных вариантах триггеров, на транзисторных схемах с 2-я

установленными состояниями, при записи бит в такую ячейку она может пребывать в

одном из состояний и сохранять бит длительное время – необходимо только питание

отсюда ее название статическая.

Достоинство: высокое

быстродействие.

Недостаток: высокое

энергопотребление, низкая удельная плотность данных так как триерная ячейка

состоит из нескольких ячеек отсюда занимают немало места на кристалле.

4. Направления повышение эффективности работы устройств ввода-вывода микропроцессорных систем.

В базовой конфигурации ПВЭМ была достигнута только 8, а позже 16 IRQ линий, а т.ж. 6 каналов ПДП/DMA причем 7 линий IRQ : 0,1,2,6,8,9,13 использовались системой, а еще 3 линии IRQ использовались Обычными Устройствами: 12 – порт манипулятора данных.

14-15- HDD (жесткие диски), т .об. оставалось 6 линий.

Если в системе использовались

Порты COM1 и COM2, то 3 и 4

т.ж. были задействованы -> оставалось 4 линии. Дальнейшее развитие ПВЭМ,

появл звук карт. Сетевые адаптеры (соот-но 5 и 10) привело к тому что осталось

2 мини IRQ7 и IRQ11. Если установить

на ПЭВМ host adapter SCSI, то он

займет линию IRQ11.

ДАльнейшее появление новых

Устройств еще более усилило эту проблему. Очевидно стало что в прежней

конфигурации развитие невозможно. Возникла потребность разработки Новой

Высокоскоростн шины для подключения новых перефер уст-в.

Многие производители

аппаратных уст-в ЭВМ такие как IBM… осознали

необходимость повышения эфф-ти настройки ПЭВМ и упрощение конфигурации ПЭВМ.

Прежде чем появл шина PSI на разных

ПЭВМ были использованы разные шины: IBM MCA, EISA. VESA VLB.

В конечном итоге компания Intel, Microsaft и ряд

др фирм смогли создать и продвинуть на рынок современный стандарт шины PCI, а т.ж. поддержку режима Plugandplay (PnP) BIOS и переф оборудования.

BIOS является ключевым элементом

системной платы, без которого все ее замечательные компоненты представляют

собой лишь набор дорогих «железок».

BIOS пользуясь средствами,

предоставляемыми чипсетом управляет всеми компонентами и ресурсами системной

платы. Отсюда следует, что используемая версия BIOS очень сильно привязана к Chipset’у. BIOS хранится в

микросхеме энергонезависимой ROMBIOS или FLASH-памяти (Flash-BIOS). В настоящее время существует 2 основных

разработчика BIOS: AMI и AWARD, которые

поставляют новые версии системных плат, которые производят окончательную

подгонку BIOS под конкретную модель

системной платы, особенности которой они лучше всех знают.

Существует вариант «горячей»

замены ROMBIOS: для этого из аналогичной работоспособной платы

извлекают микросхему BIOS и устанавливают ее вместо испорченной, затем включают

и загружают ПЭВМ в режиме перезаписи BIOS.

Опция BIOS: Boot Block Recovery,

кроме того в Setup должно быть разрешено

применение теневой памяти для области системной BIOS. Далее не выключая питания заменяют микросхему на

невернозаписанную и выполняют процедуру перезаписи, при этом ПЭВМ продолжает

работать, поскольку под BIOS

используется из теневой области ОЗУ.

Недостатки современных Flash BIOS

является подверженность поражения вирусами, причем парольная (программная)

защита может быть взломана, а надежная аппаратная защита (необходимость подачи

высокого напряжения для стирания) имеется далеко не на всех микросхемах и

системных платах.

7. Аппаратное построение последовательного канала.

Для

обмена информацией с устройствами I/o используется последовательные каналы, которые называются

камуникационными контролерами или адаптерами.

Регистровая

структура последовательного канала:

1)регистр управления:

|

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

Бит 7: вместе с битом 0 и 1 задаем режим работы последовательно

порта;

Бит 6 : направление сигнала:0- выходной, 1- входной.

Бит 5: способ контроля четности: 0-проверка на четность,

1-провнрка на нечетность.

Бит 4: девятый бит данных (асинхронный режим передачи данных);

Бит 3: 1-разрешен прием данных;

Бит 2: 1- автоматический контроль четности при асинхронном режиме

обмена;

Бит 0-1:

|

7

|

1

|

0

|

Биты

|

|

0

|

0

|

0

|

Режим

0,синхронный

режим

передачи данных

|

|

Х

|

0

|

1

|

Режим

1,асинхронный

|

|

Х

|

1

|

0

|

Режим

2,асинхронный

|

|

Х

|

1

|

1

|

Режим

3,асинхронный

|

2) регистр скорости (регистр управления обмена):

15 0

|

|

|

Бит

15:0-тактирование порта происходит от внешнего источника;

1- тактирование

порта происходит от внутреннего источника.

Бит

0-14: значение скорости обмена.

8. Цикл обмена данными в режиме по прерываниям.

В этом цикле имеется ряд специфических особенностей связанных с типом прерывания.

9. Сигнальные линии микропроцессора. Выходные

сигнальные линии микропроцессора.

В этом цикле имеется ряд специфических особенностей связанных с типом прерывания.

1. Векторные прерывания которые требуют проведения цикла чтения по магистрали.

2. Радиальные – которые не требуют цикла

Векторные:

код номера прерывания передается МП тем SLAVE, который данное прерывание запросило. Для этого МП

осуществляет цикл чтения по магистрали и получает код прерывания. Шина адреса в

этом случае не используется т.е. SLAVE запросивший

пр-ния и так знает что МП будет обращаться

именно к нему, поэтому на СМ достаточно всего одной линии запроса прерываний

устройств I-0 (SLAVEvов). Такую архитектуру имеет СМ Q-BUS.

Запрос

прерывания осуществляется сигналом VIRQ который

формируется SLAVEом. Получив VIRQ МП предоставляет

прерывания (предварительно закончив выполнение

текущей команды) далее МП выставляет сигнал DIN и сигнал предоставления прерывания IAKО. IAKO последовательно проходит ч/з все SLAVEвы, если устройство запросило прерывание то оно не

пропускает ч/з себя сигнал IAKO. Если одновременно запрос прерывания осуществляет

одно и более Уст-в, то обслуживаться

будет устр-во расположенное ближе к МП. (Географически приоритет).

Получив сигнал IAKO уст-во снимает сигнал VIRQ затем МП проводит цикл безадресного чтения номера

прерывания.

Радиального

прерывание – СистМагистр имеется столько линий запросов прерываний сколько

всего видов прерываний. Таких Об. Каждому SLAVEу поставлена в соответствие линия запроса пр-ий.

Поэтому никаких циклов обмена по СМ не

требуется. Для управления процессом обслуживания пр-ия дополнительно включается

микросхема контроллера пр-ий. Именно так организовано пр-ие в шине ISA.

Взаимодействие МП с

окружающей средой заключается в выполнении одного из двух действий:

1) МП либо выводит (записывает) данные

2)

МП считывает

данные и команды.

Для реализации вышеуказанных

действий предназначены сигнальные линии МП.

Системную шину адреса/данных

образуют 20 сигнальных линий.

Линии AD15-AD0 –

мультиплексорная двунаправленная шина адреса/данных. По ее 16-ти линиям

передаются младшие 16 бит адреса памяти (или полный адрес порта I/O) и данные

А19/ST6-A16/ST3 –

шина адреса состояния, причем сигналы распределяются:

На линиях ST4, ST3 определяется

сегментный регистр, участвующий в формировании 20-ти разрядного физического

адреса ячейки памяти.

Сигнальные линии

TEST – этот входной сигнал применяется

совместно с командой WAIT.

Команда TEST выполняет операцию логического «И» над двумя операциями и в зависимости от

результата устанавливает флаги SF, ZF и PF, при этом флаги

CF и

OF сбрасываются.

По состоянию

флажков можно судить о результатах выполнения данной команды, так как она не

изменяет значения операндов. В качестве 1-го операнда указывается регистр кроме

сегментного или ячейка памяти.

А в качестве 2-го

операнда также регистр кроме сегментного, ячейка памяти или непосредственное

значение.

Состояние флажков

Флаг SF устанавливается в 1-цу, если в результате

выполнения команды TEST

образовалось число с установленным знаковым битом.

ZF -

устанавливается в 1-цу, если в результате выполнения команды TEST образовалось число состоящее из одних 0.

PF -

устанавливается в 1-цу, если в результате выполнения команды TEST образовалось число с четным количеством

двоичных единиц.

RDY-данный сигнал определяет степень готовности внешнего

устройства к взаимодействии. с МП. Если уровень низкий то водиться поределеное

число тактов синхронизации, а при активном сигнале МП выходит из состояния

ожидания и возобновляет работу (синхронизация памяти и МП )

CLR- сброс и начальная установка

CLC-входящий сигнал, синхронизация и тактирование. На

этот вход подаются сигналы от внешнго генератора тактовых импульсов для

синхронизации всех действий МП.

MN/MX-уровень

этого сигнала определяет конфигурацию МП.

10. Архитектура контроллера прерываний. Схема

аппаратных прерываний микропроцессора.

Логически в

архитектуре контроллера прерываний можно выделить 4 основных регистра:

1.

регистр

входных запросов

2.

регистр

маски

3.

регистр

схемы приоритетов

регистр обслуживаемых запросов

Будем считать что

текущим сигналом поступающим на вход контроллера прерываний является запрос от

клавиатуры (IRQ1)

данный сигнал поступает в регистр запросов и устанавливает в 1 соответствующий

его бит, далее сигнал поступает в регистр маски 0 значение бита разрешает

дальнейшее прохождение сигнала, далее на пути сигнала находится регистр схема

анализа приоритетов, максимальный приоритет имеет таймер (IRQ0), таким образом приоритеты сигналов IRQ снижаются по мере роста № сигнала. Вопрос

о приоритетах становится важным только в том случае если очередной сигнал

прерывания приходит в тот момент когда еще не закончено выполнение программой

обработки предыдущего прерывания далее сигнал поступает в регистр обслуживания

запросов и дает разрешение на установку в 1 его бита (но не устанавливает)

одновременно с этим сигнал поступает на вход INT МП, МП регистрирует сигнал если

установлен флаг IF в

регистре флагов. Получив сигнал INT МП генерирует сигнал INTA который поступает в контроллер прерываний и выполняет там

2 действия:

1.

устанавливает

в 1 бит регистра обслуживания запросов

2.

сбрасывает

бит регистра запроса с этого момента новый сигнал IRQ1 может поставить на вход контроллера

прерываний, а текущий сигнал переводится в разряд обслуживаемых.

Сигналы внешних аппаратных

прерываний возникающие в устройствах входящих в состав УЧПУ (таймер, дисководы,

и т.д.) поступают в МП через контроллер прерываний.

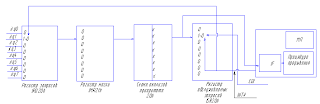

Рассмотрим схему аппаратных

прерываний с применением контроллера прерываний:

К 8-и входным каналам

контроллера прерываний подключаются выводы устройств на которых возникают

сигналы прерываний.

IRQ-запрос прерываний (Interrupt Re Quest).

Выход INT контроллера подключается к одноименному входу МП.

Таким образом основное

назначение контроллера прерываний это направление сигналов запроса прерываний с

от входных устройств на единственный вход МП.

Кроме сигнала int в МП из контроллера передается № вектора

с которым связана процедура обслуживания поступившего прерывания. № этого

вектора формируется путем сложения базового вектора (формирующегося либо при

загрузке системы или запомнен в одном из регистров) с № входной линии по

которой поступил запрос прерываний. Контроллер программирования через порты с

адресом 20h,

21h.

Рассмотрим

перечень аппаратных векторов и закрепленных за ними устройств.

Комментариев нет:

Отправить комментарий