41.Аппаратные интерфейсы микропроцессорных систем

Интерфейс – это граница

раздела 2х систем: устройств и программ, элементы соединения и вспомогат схемы

управления, используемые для соединия устр-в.

По способу передачи информации интерфейс делят на 1) параллель 2)

последоват.

В параллел – все биты

передаваемого байта/ слова выставляются и идут по параллел проводам. В современ.

ПЭВМ традиционно используется параллел интерфейс , т.к. он связан с LPT портом, шины ATA, SCSI и все шины расширения.

В последоват – биты/слова

передаются друг за другом обычно по одной или двух проводной линии. Эта линия

м.б. однонаправленной COM-порт и

двунаправл USB. Параметры интерфейса:

1. Пропускная способность. ТЕхнический

прогресс приводит к неуклонным ростам объемов передаваемой информации так

например если раньше для вывода на печать на матричном принтере вполне

обходились COM-портом, то современным лазерным принтером при высоком разрешении, больше

600dpi, уже не хватает

LPT-портов. эТОТ

же процесс касается и сканеров.

2. Контроль достоверности передачи

данных. Ветераном контроля достоверности явл шина SCSI т.к. она оснащена битом паритета

четности. Так же контроль паритета применяется в интерфейсе шины PCI. Шина ISA в этом плане беззащитна как и ее

потомок ATA , в которой до появления ультра DMA контроля достоверности не было. В

новых интерфейсах этому процессу о контроле достоверности уделяется большое

внимание особенно с учетом работы интерфейса: 1)высокая частота.2) большие

расстояния.

Контроль

достоверности может производится и на более высоком протокольном уровне

(контроль целостности пакетов) и на аппаратном уровне

3. Допустимое удаление соединяемых

устройств

Ограничение

свойств здесь связано как с частотными свойствами кабеля, так и с

помехозащитностью интерфейса . К этому включается часть помех от соседних линий

интерфейсов а т.ж. от искажения уровня сигнала.

4. Топология соединения. С появл шин USB и FIREWIRE в качестве хар-ки интер-са стала

фигурировать топология соединения. У RS232C и Centronics -2х точечная топология

Интерфейсы

шин USB реализуют древовидную топология.

5. Гальваническая развязка. ЕЕ отсутствие

приводит к появл уравновешивающего тока (если до подключ инт-са была разность

потенциалов) что приводит 1) к падению напряжения на общем проводе 2) к

смещению уровня сигнала (искажению)

6. Возможность «горячего»

подключения/отключения или замены устр-в. Данная проблема рассмотр в 2х

аспектах: 1) безопасность переключения на ходу кАк для самих устр-в и их

интерфейсных схем, так и для целостности хранящихся и передаваемых данных. 2)

возможность использования вновь

подключенных устр-в без перезапуска системы, а так же продолжение устойчивой

работы системы при отключении устр-ва

7. Реализация возможности PnP, которая предназначена для снятия с

пользователя забот по конфигурации подключенных устр-в.

42.Повышение производительности работы микропроцессорной системы. Накопители информации

Одним из способов повышения

производительности ввода/вывода является использование параллелизма путем

объединения нескольких физических дисков в матрицу (группу) с организацией их

работы аналогично одному логическому диску. К сожалению, надежность матрицы

любых устройств падает при увеличении числа устройств. Полагая интенсивность

отказов постоянной, т.е. при экспоненциальном законе распределения наработки на

отказ, а также при условии, что отказы независимы, получим, что среднее время

безотказной работы (mean time to failure - MTTF) матрицы дисков будет равно:

MTTF одного диска / Число дисков в матрице. Для достижения повышенного уровня

отказоустойчивости приходится жертвовать пропускной способностью ввода/вывода

или емкостью памяти. Необходимо использовать дополнительные диски, содержащие

избыточную информацию, позволяющую восстановить исходные данные при отказе

диска. Отсюда получают акроним для избыточных матриц недорогих дисков RAID

(redundant array of inexpensive disks). Существует несколько способов

объединения дисков RAID. Каждый уровень представляет свой компромисс между

пропускной способностью ввода/вывода и емкостью диска, предназначенной для

хранения избыточной информации. Когда

какой-либо диск отказывает, предполагается, что в течение короткого интервала

времени он будет заменен и информация будет восстановлена на новом диске с

использованием избыточной информации. Это время называется средним временем

восстановления (mean time to repair - MTTR). Этот показатель можно уменьшить,

если в систему входят дополнительные диски в качестве "горячего

резерва": при отказе диска резервный диск подключается аппаратно-программными

средствами. Периодически оператор вручную заменяет все отказавшие диски. Четыре

основных этапа этого процесса состоят в следующем:

- определение отказавшего диска,

- устранение отказа без останова обработки;

- восстановление потерянных данных на резервном диске;

43.Программная модель внешнего устройства микропроцессорной системы.

Подключение внешних устройств к системной шине осуществляется посредством электронных схем, называемых контроллерами ВВ (интерфейсами ВВ). Они согласуют уровни электрических сигналов, а также преобразуют машинные данные в формат, необходимый устройству, и наоборот. Обычно контроллеры ВВ конструктивно оформляются вместе с процессором в виде интерфейсных плат. В процессе ввода/вывода передается информация двух видов: управляющие данные (слова) и собственно данные, или данные-сообщения. Регистр, содержащий группу бит, к которой процессор обращается в операциях ВВ, образует порт ВВ. Таким образом, наиболее общая программная модель внешнего устройства, которое может выполнять ввод и вывод, содержит четыре регистра ВВ: регистр выходных данных (выходной порт), регистр входных данных (входной порт), регистр управления и регистр состояния (рис. 3.1). Каждый из этих регистров должен иметь однозначный адрес, который идентифицируется дешифратором адреса.

Непосредственные действия, связанные с

вводом/выводом, реализуются одним из двух способов, различающихся адресацией

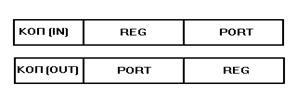

регистров ВВ. Интерфейс с изолированными

шинами характеризуется раздельной адресацией памяти и внешних устройств при

обмене информацией. Изолированный ВВ предполагает наличие специальных команд

ввода/вывода, общий формат которых показан на рис. 3.2

Нетрудно заметить, что в этом способе адресное

пространство портов ввода и вывода изолировано от адресного пространства памяти.Разделение

адресных пространств осуществляется с помощью управляющих сигналов, относящихся

к системам ВВ и памяти (MEMRD# - считывание данных из памяти, MEMWR# - запись

данных в память, IORD# - чтение порта ВВ, IOWR# - запись в порт ВВ) (# -

активный низкий уровень сигналов).

Таким образом, интерфейс с общими шинами

(ввод/вывод с отображением на память) имеет организацию, при которой часть

общего адресного пространства отводится для внешних устройств, регистры которых

адресуются так же, как и ячейки памяти. В этом случае для адресации портов ВВ

используются полные адресные сигналы: READ - чтение, WRITE - запись.

44. Архитектура таймера микропроцессора.

45.Организация сегмента стека. Привести примеры.

Таймер входит в состав

вычислителя и выполняет следующие операции:

1)прерывание МП с постоянной

частотой для того, чтобы OС ЭВМ могла

переключать выполняющие программы.

2)вывод в устройство I/o точных

временных сигналов с прогнозируемыми периодами.

3)измерения временной

задержки между внешними событиями.

4)подсчет числа событий.

5)прерывание МП после

появления запрограммированного числа событий.

Микросхема

таймера состоит из 3-х однотипных каналов, каждый из которых программируется

через порты. Данные через порт записываются в регистр I/o по байтово (сначала младшие затем старшие). Полученное

число передается в шестнадцати разрядный регистр таймера, который хранит его. В

заданный момент времени копия полученного числа записывается в 16-и разрядный

счетчик. При появлении на входе счетчика

импульса, его значение уменьшается на единицу импульсами генератора. При

достижении соответствующего значения канал выдает из выходного регистра сигнал

и новая копия содержимого входного регистра записывается в счетчик. Текущее

содержимое счетчика можно прочитать в любой момент и это не помешает таймеру

выполнить свои функции. Таймер получает импульсы с частотой 1,19318 МГц. Канал

0 – определяет время суток входные импульсы поступают через 55 мсек.(18,2 раза

в сек.) каждая из этих сигналов вызывает аппаратное прерывание IRQ0. результаты подсчета выбранных таймером

сигналов хранятся в облости переменных BIOS последующему адресу:0000:046ch. Канал 1- управляет ригинирацией памяти;

Канал 2- связан с

динамикой

Каждый канал

имеет две входные и одну выходную линию. На линиях CLK поступают

прямоугольные тактовые импульсы GATE – позволяет или запрещает прохождение

импульсов.

Порт 43h связан

8-ми размерным командным регистром микросхемы таймера. Рассмотрим

основные виды данного регистра :

Бит 0 : 0- отчет

идет в двоичной форме; в обратном случае в двоичном – десятичной(ВСД)

Бит 1…3: номер

режима выработки сигнала канала(обычно равно 3)

Бит 4…5:тип

операции с таймером.00-передача значения счетчика выходной регистр;

01-считывание /

запись только младшего байта;10- считывание /запись старшего байта;

1 1- считывание /

запись сначала младшего, затем старшего байта.

Бит 6…7: 00- нулевой канал;

01-первый канал10-второй

канал

11- подготовка к считыванию

данных из командного регистра.

Стек – это область памяти, специально выделенная для временного хранения параметров или программных данных, необходимых для информационной связи программ и процедур.

Рассмотрим сегмент стека:

Количество стеков памяти ЭВМ ограничивается выделенной областью памяти. Максимальная область стека для текущего МП равно 64 Kb. Поскольку существует только 1 регистр сегмента стека (SS), то в каждый момент времени можно обращаться только к 1 стеку. Вершина стека SP используется для хранения адреса последнего члена последовательности, записанных в стек.

Существуют 2 основные команды, предназначенные для работы со стеком:

1) push <операнд> - запись операнда в стек

push AX – кладем текущее содержание регистра AX в стек по адресу из регистра SP

2) pop <операнд> - считать данные из текущей вершины стека в операнд

pop AX – считаем по адресу из регистра SP в AX,

Запись данных в стек называется операцией загрузки. При загрузке числа в стек содержимое регистра SP уменьшается на слово – указывает на новую вершину стека.

Чтение данных, начиная с вершины стека называется операцией считывания, при которой содержимое регистра SP увеличивается на слово.

При этом считается что ячейка стека, содержащая считанное число является свободным и готово для последующего использования.

46.BIOS Setup. Назначение и функции.

Все современные ПЭВМ имеют утилиту SETUP, встроенную в ROMBIOS. Утилита BIOSSETUP имеет интерфейс в виде Menu. Для входа в SETUP во время выполнения POST появляется предложение нажать клавишу Del, иногда Esc или Ctrl+Esc. Предложение F1 входа в Setup появляется, если POST обнаружит ошибку оборудования, которая может быть устранена посредством Setup.

Standard CMOS Setup (Установка стандартных параметров CMOS)

Data, время

Разрешение переключения на летнее/зимнее время

Тип Harddisk C:

0 – применяется при отсутствии HDD (исключение), а также для SCSI

1-46 – задание фиксированных параметров

47 – параметры, определяемые пользователем или утилитой IDE Auto Detection

Тип HDD D: аналогично диску C:

Primary Slave тип жестких дисков, подключенных к первич-

Secondary Master ному или вторичному контроллеру IDE, распо-

Secondary Slave ложенному на системной плате

Floppy Drive A – Тип НГМД с физическим адресом А: (подключен к разъему с перевернутой частью шлейфа

Primary Display – Mono, CGA, VGA

Keyboard – Разрешение теста клавиатуры (Not Installed) – позволяет загружать сервер с отключенной Клавой

Halt on Error – список ошибок разрешения остановок при выполнении POST (ожидание нажатия клавиши F1)

Advanced CMOS Setup

Above 1Mb Memory test – разрешение тестирования памяти свыше 1 Мб. Запрет ускоряет прохождение POST, при этом память свыше 1 Мб не тестируется, а только инициализируется. Если HIMEM.SYS, то тестирование области памяти происходит гораздо эффективнее, чем в POST

Quick Boot – разрешение быстрой загрузки (память свыше 1 Мб не тестируется, готовность HDD проводится с минимальным временем)

System Boot Up Numlock – состояние индикатора для использования цифрового поля клавиатуры после загрузки

Floppy Drive Swap – разрешение взаимной замены имен дисков A: и B:

System Boot Sequence – последовательность опроса дисков при загрузке

Boot Sector Virus (Protection Virus Warning) – Разрешение антивирусной защиты

External Cache Memory – разрешение работы L2 кэша.

Internal Cache Memory – разрешение работы L1 кэша.

Memory Parity

Chipset Setup – Управление особенностями Chipset’a

Power Management – управление режимом энергосбережения

Время и уровни «засыпания», события, вызывающие «пробеждения», режимы работы, в частности DozeMode (20% от частоты процессора), StandBy (8% от частоты процессора), SuspendMode (1%)

PCI Setup Plug and Play – Конфигурирование распределения ресурсов

Peripheral Setup – Конфигурирование периферии системной платы

Регулировка портов

Разрешение и т.д.

47.Цикл программного обмена данными (ISA).

ISA (от англ. Industry Standard Architecture, ISA bus, произносится как ай-эс-эй) — 8- или 16-разрядная шина ввода/вывода IBM PC-совместимых компьютеров. Служит для подключения плат расширения стандарта ISA. Конструктивно выполняется в виде 62-х или 98-контактного разъёма на материнской плате.

С появлением материнских плат формата ATX шина ISA перестала широко использоваться в компьютерах, хотя встречаются ATX-платы с AGP 4x, 6 PCI и одним (или двумя) разъёмами ISA. Но пока её ещё можно встретить в старых AT-компьютерах, а также в промышленных компьютерах.

Для встроенных систем существует вариант компоновки шины ISA, отличающийся применяемыми разъёмами — шина PC/104.

С появлением материнских плат формата ATX шина ISA перестала широко использоваться в компьютерах, хотя встречаются ATX-платы с AGP 4x, 6 PCI и одним (или двумя) разъёмами ISA. Но пока её ещё можно встретить в старых AT-компьютерах, а также в промышленных компьютерах.

Для встроенных систем существует вариант компоновки шины ISA, отличающийся применяемыми разъёмами — шина PC/104.

48.Классификация протоколов локальных вычислительных сетей. Описание уровней протокола TCP/IP.

Стек протоколов TCP/IP (англ. Transmission Control Protocol/Internet Protocol — протокол управления передачей) — набор сетевых протоколов разных уровней модели сетевого взаимодействия DOD, используемых в сетях. Протоколы работают друг с другом в стеке (англ. stack, стопка) — это означает, что протокол, располагающийся на уровне выше, работает «поверх» нижнего, используя механизмы инкапсуляции. Например, протокол TCP работает поверх протокола IP.

Стек протоколов TCP/IP основан на модели сетевого взаимодействия DOD и включает в себя протоколы четырёх уровней:

прикладного (application),

транспортного (transport),

сетевого (network),

канального (data link).

Протоколы этих уровней полностью реализуют функциональные возможности модели OSI. На стеке протоколов TCP/IP построено всё взаимодействие пользователей в IP-сетях. Стек является независимым от физической среды передачи данных.

Стек протоколов TCP/IP основан на модели сетевого взаимодействия DOD и включает в себя протоколы четырёх уровней:

прикладного (application),

транспортного (transport),

сетевого (network),

канального (data link).

Протоколы этих уровней полностью реализуют функциональные возможности модели OSI. На стеке протоколов TCP/IP построено всё взаимодействие пользователей в IP-сетях. Стек является независимым от физической среды передачи данных.

Уровни стека TCP/IP

Существуют разногласия в том, как вписать модель TCP/IP в модель OSI, поскольку уровни в этих моделях не совпадают.

К тому же, модель OSI не использует дополнительный уровень — «Internetworking» — между транспортным и сетевым уровнями. Примером спорного протокола может быть ARP или STP.

Вот как традиционно протоколы TCP/IP вписываются в модель OSI:

Распределение протоколов по уровням модели OSI7 Прикладной напр., HTTP, SMTP, SNMP, FTP, Telnet, SSH, SCP, SMB, NFS, RTSP, BGP

6 Представления напр., XDR, AFP, TLS, SSL

5 Сеансовый напр., ISO 8327 / CCITT X.225, RPC, NetBIOS, PPTP, L2TP, ASP

4 Транспортный напр., TCP, UDP, SCTP, SPX, RTP, ATP, DCCP, GRE

3 Сетевой напр., IP, ICMP, IGMP, CLNP, OSPF, RIP, IPX, DDP, ARP, RARP

2 Канальный напр., Ethernet, Token ring, HDLC, PPP, X.25, Frame relay, ISDN, ATM, MPLS

1 Физический напр., электрические провода, радиосвязь, волоконно-оптические провода, Wi-Fi

Обычно в стеке TCP/IP верхние 3 уровня (прикладной, представительский и сеансовый) модели OSI объединяют в один — прикладной. Поскольку в таком стеке не предусматривается унифицированный протокол передачи данных, функции по определению типа данных передаются приложению. Упрощенно интерпретацию стека TCP/IP можно представить так:

Распределение протоколов по уровням модели TCP/IP5 Прикладной

«7 уровень» напр., HTTP, RTP, FTP, DNS

(RIP, работающий поверх UDP, и BGP, работающий поверх TCP, являются частью сетевого уровня)

4 Транспортный напр., TCP, UDP, SCTP, DCCP

(протоколы маршрутизации, подобные OSPF, что работают поверх IP, являются частью сетевого уровня)

3 Сетевой Для TCP/IP это IP (IP)

(вспомогательные протоколы, вроде ICMP и IGMP, работают поверх IP, но тоже относятся к сетевому уровню; протокол ARP является самостоятельным вспомогательным протоколом, работающим поверх физического уровня)

2 Канальный Ethernet, IEEE 802.11 Wireless Ethernet, SLIP, Token Ring, ATM и MPLS

1 Физический напр., физическая среда и принципы кодирования информации, T1, E1

[править]

Физический уровень

Физический уровень описывает среду передачи данных (будь то коаксиальный кабель, витая пара, оптическое волокно или радиоканал), физические характеристики такой среды и принцип передачи данных (разделение каналов, модуляцию, амплитуду сигналов, частоту сигналов, способ синхронизации передачи, время ожидания ответа и максимальное расстояние).

[править]

Канальный уровень

Канальный уровень описывает, каким образом передаются пакеты данных через физический уровень, включая кодирование (то есть специальные последовательности бит, определяющих начало и конец пакета данных). Ethernet, например, в полях заголовка пакета содержит указание того, какой машине или машинам в сети предназначен этот пакет.

Примеры протоколов канального уровня — Ethernet, IEEE 802.11 Wireless Ethernet, SLIP, Token Ring, ATM и MPLS.

PPP не совсем вписывается в такое определение, поэтому обычно описывается в виде пары протоколов HDLC/SDLC.

MPLS занимает промежуточное положение между канальным и сетевым уровнем и, строго говоря, его нельзя отнести ни к одному из них.

Канальный уровень иногда разделяют на 2 подуровня — LLC и MAC.

[править]

Сетевой уровень

Сетевой уровень изначально разработан для передачи данных из одной (под)сети в другую. Примерами такого протокола является X.25 и IPC в сети ARPANET.

С развитием концепции глобальной сети в уровень были внесены дополнительные возможности по передаче из любой сети в любую сеть, независимо от протоколов нижнего уровня, а также возможность запрашивать данные от удалённой стороны, например в протоколе ICMP (используется для передачи диагностической информации IP-соединения) и IGMP (используется для управления multicast-потоками).

ICMP и IGMP расположены над IP и должны попасть на следующий — транспортный — уровень, но функционально являются протоколами сетевого уровня, и поэтому их невозможно вписать в модель OSI.

Пакеты сетевого протокола IP могут содержать код, указывающий, какой именно протокол следующего уровня нужно использовать, чтобы извлечь данные из пакета. Это число — уникальный IP-номер протокола. ICMP и IGMP имеют номера, соответственно, 1 и 2.

К этому уровню относятся: DHCP[1], DVMRP, ICMP, IGMP, MARS, PIM, RIP, RIP2, RSVP

[править]

Транспортный уровень

Протоколы транспортного уровня могут решать проблему негарантированной доставки сообщений («дошло ли сообщение до адресата?»), а также гарантировать правильную последовательность прихода данных. В стеке TCP/IP транспортные протоколы определяют, для какого именно приложения предназначены эти данные.

Протоколы автоматической маршрутизации, логически представленные на этом уровне (поскольку работают поверх IP), на самом деле являются частью протоколов сетевого уровня; например OSPF (IP идентификатор 89).

TCP (IP идентификатор 6) — «гарантированный» транспортный механизм с предварительным установлением соединения, предоставляющий приложению надёжный поток данных, дающий уверенность в безошибочности получаемых данных, перезапрашивающий данные в случае потери и устраняющий дублирование данных. TCP позволяет регулировать нагрузку на сеть, а также уменьшать время ожидания данных при передаче на большие расстояния. Более того, TCP гарантирует, что полученные данные были отправлены точно в такой же последовательности. В этом его главное отличие от UDP.

UDP (IP идентификатор 17) протокол передачи датаграмм без установления соединения. Также его называют протоколом «ненадёжной» передачи, в смысле невозможности удостовериться в доставке сообщения адресату, а также возможного перемешивания пакетов. В приложениях, требующих гарантированной передачи данных, используется протокол TCP.

UDP обычно используется в таких приложениях, как потоковое видео и компьютерные игры, где допускается потеря пакетов, а повторный запрос затруднён или не оправдан, либо в приложениях вида запрос-ответ (например, запросы к DNS), где создание соединения занимает больше ресурсов, чем повторная отправка.

И TCP, и UDP используют для определения протокола верхнего уровня число, называемое портом.

См. также: Список портов TCP и UDP

[править]

Прикладной уровень

На прикладном уровне работает большинство сетевых приложений.

Эти программы имеют свои собственные протоколы обмена информацией, например, HTTP для WWW, FTP (передача файлов), SMTP (электронная почта), SSH (безопасное соединение с удалённой машиной), DNS (преобразование символьных имён в IP-адреса) и многие другие.

В массе своей эти протоколы работают поверх TCP или UDP и привязаны к определённому порту, например:

HTTP на TCP-порт 80 или 8080,

FTP на TCP-порт 20 (для передачи данных) и 21 (для управляющих команд),

SSH на TCP-порт 22,

запросы DNS на порт UDP (реже TCP) 53,

обновление маршрутов по протоколу RIP на UDP-порт 520.

Эти порты определены Агентством по выделению имен и уникальных параметров протоколов (IANA).

К этому уровню относятся: Echo, Finger, Gopher, HTTP, HTTPS, IMAP, IMAPS, IRC, NNTP, NTP, POP3, POPS, QOTD, RTSP, SNMP, SSH, Telnet, XDMCP.

Существуют разногласия в том, как вписать модель TCP/IP в модель OSI, поскольку уровни в этих моделях не совпадают.

К тому же, модель OSI не использует дополнительный уровень — «Internetworking» — между транспортным и сетевым уровнями. Примером спорного протокола может быть ARP или STP.

Вот как традиционно протоколы TCP/IP вписываются в модель OSI:

Распределение протоколов по уровням модели OSI7 Прикладной напр., HTTP, SMTP, SNMP, FTP, Telnet, SSH, SCP, SMB, NFS, RTSP, BGP

6 Представления напр., XDR, AFP, TLS, SSL

5 Сеансовый напр., ISO 8327 / CCITT X.225, RPC, NetBIOS, PPTP, L2TP, ASP

4 Транспортный напр., TCP, UDP, SCTP, SPX, RTP, ATP, DCCP, GRE

3 Сетевой напр., IP, ICMP, IGMP, CLNP, OSPF, RIP, IPX, DDP, ARP, RARP

2 Канальный напр., Ethernet, Token ring, HDLC, PPP, X.25, Frame relay, ISDN, ATM, MPLS

1 Физический напр., электрические провода, радиосвязь, волоконно-оптические провода, Wi-Fi

Обычно в стеке TCP/IP верхние 3 уровня (прикладной, представительский и сеансовый) модели OSI объединяют в один — прикладной. Поскольку в таком стеке не предусматривается унифицированный протокол передачи данных, функции по определению типа данных передаются приложению. Упрощенно интерпретацию стека TCP/IP можно представить так:

Распределение протоколов по уровням модели TCP/IP5 Прикладной

«7 уровень» напр., HTTP, RTP, FTP, DNS

(RIP, работающий поверх UDP, и BGP, работающий поверх TCP, являются частью сетевого уровня)

4 Транспортный напр., TCP, UDP, SCTP, DCCP

(протоколы маршрутизации, подобные OSPF, что работают поверх IP, являются частью сетевого уровня)

3 Сетевой Для TCP/IP это IP (IP)

(вспомогательные протоколы, вроде ICMP и IGMP, работают поверх IP, но тоже относятся к сетевому уровню; протокол ARP является самостоятельным вспомогательным протоколом, работающим поверх физического уровня)

2 Канальный Ethernet, IEEE 802.11 Wireless Ethernet, SLIP, Token Ring, ATM и MPLS

1 Физический напр., физическая среда и принципы кодирования информации, T1, E1

[править]

Физический уровень

Физический уровень описывает среду передачи данных (будь то коаксиальный кабель, витая пара, оптическое волокно или радиоканал), физические характеристики такой среды и принцип передачи данных (разделение каналов, модуляцию, амплитуду сигналов, частоту сигналов, способ синхронизации передачи, время ожидания ответа и максимальное расстояние).

[править]

Канальный уровень

Канальный уровень описывает, каким образом передаются пакеты данных через физический уровень, включая кодирование (то есть специальные последовательности бит, определяющих начало и конец пакета данных). Ethernet, например, в полях заголовка пакета содержит указание того, какой машине или машинам в сети предназначен этот пакет.

Примеры протоколов канального уровня — Ethernet, IEEE 802.11 Wireless Ethernet, SLIP, Token Ring, ATM и MPLS.

PPP не совсем вписывается в такое определение, поэтому обычно описывается в виде пары протоколов HDLC/SDLC.

MPLS занимает промежуточное положение между канальным и сетевым уровнем и, строго говоря, его нельзя отнести ни к одному из них.

Канальный уровень иногда разделяют на 2 подуровня — LLC и MAC.

[править]

Сетевой уровень

Сетевой уровень изначально разработан для передачи данных из одной (под)сети в другую. Примерами такого протокола является X.25 и IPC в сети ARPANET.

С развитием концепции глобальной сети в уровень были внесены дополнительные возможности по передаче из любой сети в любую сеть, независимо от протоколов нижнего уровня, а также возможность запрашивать данные от удалённой стороны, например в протоколе ICMP (используется для передачи диагностической информации IP-соединения) и IGMP (используется для управления multicast-потоками).

ICMP и IGMP расположены над IP и должны попасть на следующий — транспортный — уровень, но функционально являются протоколами сетевого уровня, и поэтому их невозможно вписать в модель OSI.

Пакеты сетевого протокола IP могут содержать код, указывающий, какой именно протокол следующего уровня нужно использовать, чтобы извлечь данные из пакета. Это число — уникальный IP-номер протокола. ICMP и IGMP имеют номера, соответственно, 1 и 2.

К этому уровню относятся: DHCP[1], DVMRP, ICMP, IGMP, MARS, PIM, RIP, RIP2, RSVP

[править]

Транспортный уровень

Протоколы транспортного уровня могут решать проблему негарантированной доставки сообщений («дошло ли сообщение до адресата?»), а также гарантировать правильную последовательность прихода данных. В стеке TCP/IP транспортные протоколы определяют, для какого именно приложения предназначены эти данные.

Протоколы автоматической маршрутизации, логически представленные на этом уровне (поскольку работают поверх IP), на самом деле являются частью протоколов сетевого уровня; например OSPF (IP идентификатор 89).

TCP (IP идентификатор 6) — «гарантированный» транспортный механизм с предварительным установлением соединения, предоставляющий приложению надёжный поток данных, дающий уверенность в безошибочности получаемых данных, перезапрашивающий данные в случае потери и устраняющий дублирование данных. TCP позволяет регулировать нагрузку на сеть, а также уменьшать время ожидания данных при передаче на большие расстояния. Более того, TCP гарантирует, что полученные данные были отправлены точно в такой же последовательности. В этом его главное отличие от UDP.

UDP (IP идентификатор 17) протокол передачи датаграмм без установления соединения. Также его называют протоколом «ненадёжной» передачи, в смысле невозможности удостовериться в доставке сообщения адресату, а также возможного перемешивания пакетов. В приложениях, требующих гарантированной передачи данных, используется протокол TCP.

UDP обычно используется в таких приложениях, как потоковое видео и компьютерные игры, где допускается потеря пакетов, а повторный запрос затруднён или не оправдан, либо в приложениях вида запрос-ответ (например, запросы к DNS), где создание соединения занимает больше ресурсов, чем повторная отправка.

И TCP, и UDP используют для определения протокола верхнего уровня число, называемое портом.

См. также: Список портов TCP и UDP

[править]

Прикладной уровень

На прикладном уровне работает большинство сетевых приложений.

Эти программы имеют свои собственные протоколы обмена информацией, например, HTTP для WWW, FTP (передача файлов), SMTP (электронная почта), SSH (безопасное соединение с удалённой машиной), DNS (преобразование символьных имён в IP-адреса) и многие другие.

В массе своей эти протоколы работают поверх TCP или UDP и привязаны к определённому порту, например:

HTTP на TCP-порт 80 или 8080,

FTP на TCP-порт 20 (для передачи данных) и 21 (для управляющих команд),

SSH на TCP-порт 22,

запросы DNS на порт UDP (реже TCP) 53,

обновление маршрутов по протоколу RIP на UDP-порт 520.

Эти порты определены Агентством по выделению имен и уникальных параметров протоколов (IANA).

К этому уровню относятся: Echo, Finger, Gopher, HTTP, HTTPS, IMAP, IMAPS, IRC, NNTP, NTP, POP3, POPS, QOTD, RTSP, SNMP, SSH, Telnet, XDMCP.

49.Шины микропроцессорной системы и общая характеристика циклов обмена.

Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд.

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Понятно, что за один цикл обмена по 64-разрядной шине может передаваться 8 байт информации, а по 8-разрядной — только один байт. Разрядность шины данных определяет и разрядность всей магистрали. Например, когда говорят о 32-разрядной системной магистрали, подразумевается, что она имеет 32-разрядную шину данных.

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65 536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП ). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями).

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот. В большинстве случаев уровни сигналов на шинах — ТТЛ.

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса / данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 2.1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Рис. 2.1. Мультиплексирование шин адреса и данных.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных ;

Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис. 2.2):

При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Понятно, что за один цикл обмена по 64-разрядной шине может передаваться 8 байт информации, а по 8-разрядной — только один байт. Разрядность шины данных определяет и разрядность всей магистрали. Например, когда говорят о 32-разрядной системной магистрали, подразумевается, что она имеет 32-разрядную шину данных.

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65 536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП ). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями).

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот. В большинстве случаев уровни сигналов на шинах — ТТЛ.

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса / данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 2.1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Рис. 2.1. Мультиплексирование шин адреса и данных.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных ;

Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис. 2.2):

При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Комментариев нет:

Отправить комментарий