21. Процедуры межсегментного вызова и возврата,

использующие сегмент стека. Вложенные процедуры вызова и возврата. Привести

примеры.

Программа

может передавать управление процедуре находящейся в любом месте оперативной

памяти, используя при этом межсегментную команду CALL.

Исполняя

данную команду МП выполняет следующие действия:

1)

SP уменьшается

на слово, при этом содержимое регистра CS ($ текущего кода программы) переносится в ячейку –

вершину стека.

2)

SP уменьшается

на слово снова и в стек загружается адрес команды следующей за командой CALL.

Последней

командой выполненной перед выходом из процедуры должна быть межсегментная команда

RET.

Директивы

для идентификации команды CALL является FAR.

Пример:

Push CX

Push DX

Mov DL,00

CALL 0300

Inc DL; DL=DL+1

Pop DX

Pop CX

RET

Сохраняем

последовательно CX и DX затем DX обнуляем.

В

данной процедуре инструкции считывания расположены по отношению к инструкциям

записи в обратном порядке. Сохранение и восстановление регистров CX и DX позволяет

изменять их значения не только в основной программе, но и внутри процедуры по

адресу 0300.

На

практике как правило встречаются случаи сочетания внутри межсегментных процедур.

В этом случае такие процедуры определяются как вложенные процедуры вызова.

Благодаря

стеку при использовании вложенных процедур не нарушается требуемый порядок при

завершении их работы.

22. Последовательный канал. Синхронный режим

передачи данных.

Основные отличия режима синхронный передачи данных от асинхронной состоят в том что прием / передачи данных осуществляется с помощью специальных синхронизирующих сигналов (скорость передачи выше в два и более раз).

23. Внешние прерывания микропроцессора.

Основные отличия режима синхронный передачи данных от асинхронной состоят в том что прием / передачи данных осуществляется с помощью специальных синхронизирующих сигналов (скорость передачи выше в два и более раз).

Временная

диаграмма передачи одного кадра данных

по последовательному каналу:

Схема

последовательного канала:

WR-аппаратный

сигнал кадровой синхронизации;

RG-регистр

сдвига;

D0…D7-исходные данные;

Q0…Q7-последовательные данные для передачи.

Основные отличия режима

синхронной передачи данных от режимов асинхронной передачи состоит в том, что

прием и передача осуществляется с помощью специальных синхронных сигналов.

Данный режим в настоящее время применяется для сопряжения контроллеров с

внешними регистрами сдвига, а так же для расширения ввода – вывода.

Считается данный режим более

быстрый.

23. Внешние прерывания микропроцессора.

В

современных МП есть 2 входа для внешних прерываний: INT (внешние маскируемые прерывания) NMI (внешние немаскируемые прерывания).

На

вход INT МП подключается выход программного контроля прерывания,

на вход которого подаются запросы прерываний от периферийных устройств. С точки

зрения программирования контроллер прерываний можно рассматривать как порт

ввода/вывода, в котором фиксируется код типа прерывания.

Когда

сигнал INT активен действия МП зависят от состояния флажка IF. Однако, до завершения текущей команды МП не

предпринимает никаких действий.

Примечания: имеется несколько случаев когда сигнал INT не распознается и до завершения следующей команды.

Например MOVE, IRET, POP, т.е.

команды, передающие данные в сегментный регистр. Такой механизм защищает

текущую программу, которая переходит к новому стеку путем изменения содержимого

регистров SS, SP. Если бы прерывания распознавались после модификации

регистра SS до модификации регистра SP МП включал бы содержимое регистров флагов CS и IP в

неправильную область памяти.

Если

флажок IF сброшен, т.е. прерывание по коду INT замаскировано и МП игнорирует запрос прерывания и

перехода к выполнению следующей команды.

Кроме

того в контролере прерываний можно замаскировать сигналы от отдельных

периферийных устройств. Например от Клавы, таймера, порта I/O и т.п.

Если

МП подтверждает запрос прерывания то выполняется 2 действия (послед-х цикла INT):

1)

подтверждение прерывания, т.е. восприятие запроса.

2)

контроллер подает на шину данных байт кода прерывания, который ассоциируется с

запрашиваемым к обслуживанию периферийным устройством.

МП

анализирует код типа прерывания и вызывает процедуру обслуживания данного

прерывания.

Вход

NMI применяется

для сигнализации МП об катастрофических событиях которые требуют немедленной

реакции. Например аварийное выключение сети, ошибка в тесте памяти, ошибка в

паритете при тесте памяти и т.д.

Запросы по входу NMI нельзя запретить, они запоминаются в МП и имеют более высокий

приоритет, чем прерывания по входу INT. Немаскируемые прерывания имеют фиксированный код прерывания = 2.

Вследствие чего в ответ на сигнал NMI циклы INTA не

формируются => достигается ускоренная реакция МП на это прерывание.

24. Режимы адресации портов ввода-вывода.

Привести примеры.

Современные МП системы имеют

достаточный набор средств I/O

- большое адресное пространство I/O, изолированное

от пространства памяти

- Специальные команды I/O, которые

передают данные между регистрами МП и портами I/O

Устройство управления МП при наличии

таких специальных команд генерирует управляющие сигналы, определяющие выбор

пространства I/O. Размер адресного пространства I/O равен 64 Kb. Допускается организация I/O отображено на

основную память. Цель этого отображения использование всей системы команд и

режимов адресации памяти.

Основные специальные команды:

IN (ввод)

OUT (вывод)

Данные команды передают байты

или слово между аккумулятором и адресными портами.

Пространство I/O не

сегментируется. Для обращения к порту шинный интерфейс помещает 16-bit-й адрес порта на младшие 16 линий шины адреса

слэш-данных. А 8 bit адрес порта дублируется на

линиях старшей и младшей половин этой шины.

Существует прямая и косвенная адресация портов I/O

А) прямая

Б) косвенная

Примеры

1) In AL,60h; ввод байта из порта с адр. 60h результат в AL

(прям.)

2) Mov DX 3D5h; размещ-е в DX адрес порта

In AX DX; ввод слова из порта DX в AX (косв.)

3) Out 61h,AL; вывод байта в порт с адр. 61h из AL (прям.)

4) Mov DX,3CEh; адрес порта в DX

Mov AL,5;

выводимые данные

Out DX ,AL ; вывод байта из AL

25. Организация памяти микропроцессора.

Физические и логические адреса. Привести примеры.

Основной

логической единицей памяти является сегмент, размер которого для базовой конфигурации

равен 64 кб. Сегмент представ собой сложные ячейки памяти и является

независимой и отдельно адресуемой единицей памяти. Каждому сегменту программой

назначается базовый (начальный) адрес, являющийся адресом его первого в общем адресном пространстве памяти.

Одновременно МП

адресует 4 текущих сегмента:

1) сегмент кода

программы (64 кб) в регистре CS,

2) сегмент

данных (64 кб) в регистре DS,

3) сегмент

стеков (64 кб) в регистре SS ,

4)

дополнительный сегмент данных (64 кб) в регистре ES. Взаимно сегменты в памяти

могут располагаться следующим образом

Логический и физический адреса.

Логический

адрес состоит из двух 16 битовых без знаковых значений: 1)начальный адрес

сегмента или параграф стека, 2)внутрисегментное смещение. Для любой ячейки

памяти параграф сегмента определяет первый байт содержащего ее сегмент т.е. начало сегмента, а смещение определяет расстояние в байтах от начала,

сегмента до текущей ячейки. Нулевое смещение имеет байт с наименьшим

внутрисегментным адресом, а максимальное смещение равняется FFFFh т.е. кб.

Когда устройство ШИ обращается к памяти для выборки команды или

считывания/записи данных оно образует из логического физический адрес.

Физический адрес представляет собой 20 битовое значение от 0 до FFFFFh, которое

однозначно определяет положение ячейки памяти в пространстве 1 Мб. Шина адреса

из 20 сигнальных линий Макс 220=1 Мб. Чтобы 16®20 для этого параграф сегмента сдвигается влево на 4

бита и суммируется с внутрисегментным смещением.

В структуре памяти есть 2

зарезервированные области:

1)область связанная с

выполнением процедур обслуживания прерываний (занимает первые 128 байт, а

физический адрес находится в диапазоне 00000h¸0007Fh),

2) область связанная с функцией

сброса операционной системы (последние 16 байт, физические адреса: FFFF0-FFFFFh). Данные

области использовать для других целей нельзя!!!!

26. Кэширование оперативной памяти в микропроцессорных

системах.

Выше отмечалось, что в

современных ПЭВМ стала проявляться тенденция, которая заключается в различии

параметров тактовой частоты МП и возможности микросхем динамической памяти.

Для ликвидации данной

проблемы было введено компромиссное решение, сочетающее большой обхем памяти DRAM с относительно небольшой кэш-памятью на

быстродействующих статических микросхемах памяти.

В переводе слово «Cache» - склад (тайник). Таким образом кэш применительно к

памяти представляет собой дополнительное и быстродействующее хранилище копий

блоков информации основной памяти DRAM, к

которым будет реализовано обращение из прикладной программы.

Кэш не может хранить копию всей

основной памяти, поскольку его объем во много раз меньше объема SDRAM.

Кэш хранит лишь ограниченное

количество блоков данных и каталог «Кэш-Directory» - включающий список соответствия блоков памяти и

КЭШа.

Для МП Pentium кэшируются как правило первые 64Мб SDRAM.

При каждом обращении

кэш-памяти контроллер данной кэш-памяти по каталогу проверяет есть ли копия

затребованных данных в кэше. Если таковая имеется, то обращение заданными

происходит только к кэш-памяти. Если копии нет, то данные берутся из SDRAM, причем блок данных считанных из SDRAM замещает один из блоков КЭШа.

В современных ПЭВМ обычно

строится по двухуровневой системе:

- Первичный кэш L1 кэш – встроен во все процессоры класса Intel 486 и выше, объем 8-32 кб, быстродействие его таково,

что он работает на внутренней тактовой частоте МП CPU Clock; обычно

реализуется внутри МП

-Вторичный кэш L2 кэш – обычно устанавливается на системной плате,

типовым для ПЭВМ начиная с I 486 считается

объем КЭШа 64-256, а для МП Pemtium 256-512

кб. Новые Чипсеты поддерживают вторичный кэш до 2 Мб.

- Кэш-контроллер обеспечивает

согласованность данных кэш-памяти двух уровней с данными SDRAM, причем обращение к этим данным может производиться

не только со стороны МП, но и со стороны других адаптеров, подключенных к шинам

PCI и ISA.

Контролер кэша оперирует

строкам фиксированной длины. Строка хранит блок основной памяти.

Строка может быть:

1)

действительной –

это означает, что в текущий момент времени она действительно отражает

соответствующий блок основной памяти

2)

недействительной

– она (строка) пуста.

Информация

о том, какой именно блок памяти занимает строку КЭШа называется тэгом (tag), а память tagRAM. В

настоящее время, в зависимости от способа определения взаимного соответствия

между блоком памяти и строкой КЭШа различают 3 архитектуры кэш-памяти:

1)

Полностью

ассоциированный кэш

2)

Частично

ассоциированный кэш

3)

Кэш прямого

отображения

Кэш прямого отображения

Рассмотрим принцип работы,

например, кэша объемом 256 кб с размеров строки 32б и объемом кэшируемой памяти

64 Мб.

256кб/32=8Кбайт строк (8

Кстрок)

Архитектура прямого

отображения подразумевает, что каждая строка кэша может отображать из любой

страницы кэшируемой основной памяти только соостветствующую ей строку (т.е. на

рис. Они находятся на одном горизонтальном уровне.

Номер строки в кэш-каталоге

называется индексом и в соответствии определяется битом действительности.

Если в начале каждого цикла

обращения к кэш-памяти выясняется, что требуемый блок не находится в кэше, то

генерируется цикл промаха.

Если же блок есть в кэше, то

запрос обслуживается кэш-памятью.

В цикле промаха после

считывания основной памяти новые данные помещаются в строку кэша, а в

кэш-каталог помещается номер страницы и устанавливается бит действительности.

27. Структура

EXE- и COM-программ. Привести примеры.

Программы типа .COM отличаются от программ .EXE тем, что содержат лишь один сегмент, включающий все компоненты программ: программный код (т.е. оттранслированные в машинные коды инструкции ассемблера), данные и стек. В программе нет необходимости инициализировать сегментные регистры (DS,SS и ES). Сегмент данных, как и остальные сегментные регистры, инициализируется автоматически, операционной системой.

О б р а б о т к а. Для программ в EXE и COM форматах

выполняется ассемблирование

для получения OBJ-файла, и

компоновка для получения EXE-файла. Если программа создается для выполнения как EXE-файл, то ее уже можно выполнить. Если же программа создается для выполнения

как COM-файл, то компоновщиком будет выдано сообщение:

Программы типа .COM отличаются от программ .EXE тем, что содержат лишь один сегмент, включающий все компоненты программ: программный код (т.е. оттранслированные в машинные коды инструкции ассемблера), данные и стек. В программе нет необходимости инициализировать сегментные регистры (DS,SS и ES). Сегмент данных, как и остальные сегментные регистры, инициализируется автоматически, операционной системой.

В отличие от ехе-программы сом-программа создавать

обязательный заголовок загрузки при помощи, которого загрузчик ОС ЭВМ осуществует

данной программы.

поэтому вначале сом-программ должна быть директива ORG_007h, IP=100h

В отличие от ехе-программ нет необходимости

инициализировать сегмент данных с параграфом DS, поскольку его как и другие сегментные регистры

инициализирует сама система. В связи с этим наборы данных приемы могут

размещаться как в начале так и после главной процедуры. Следовательно, иметь в

виду что необходимо указать точку входа в программу, сразу за инструкцией ORG100h: например jmp Entry.

Данные можно

разместить внутри программной процедуры. Следует иметь ввиду, что при загрузке

программы регистр IP инициализируется число 100h. После

оператора ORG 100h должна стоять первая выполнимая команда. Основные

различия между программами в EXE и COM файлах.

Р а з м е р п р о г р а м м ы. EXE-программа может

иметь любой размер, в то время

как COM-файл ограничен размером одного сегмента

и не превышает 64К. COM-файл

всегда меньше, чем соответствующий EXE-файл;

одна из причин этого - отсутствие в COM-файле 512-байтового

начального блока EXE-файла.

С е г м е н т с т е к а. В EXE-программе определяется сегмент стека, в то время как COM-программа генерирует стек автоматически. Таким образом при создании

ассемблерной программы, которая

будет преобразована в COM-файл,

стек должен быть опущен.

С е г м е н т д а н н ы х.

В EXE программе обычно

определяется сегмент данных, а регистр DS инициализируется адресом этого

сегмента. В COM-программе все данные должны быть определены

в сегменте кода.

Ниже будет показан простой способ решения этого вопроса.

И н и ц и а л и з а ц и я. EXE-программа

записывает нулевое слово в стек и

инициализирует регистр DS. Так как COM-программа не имеет ни стека, ни сегмента данных, то

эти шаги отсутствуют. Когда COM-программа начинает работать, все сегментные

регистры содержат адрес

префикса программного сегмента (PSP), 256-байтового (шест. 100) блока, который

резервируется операционной системой DOS непосредственно перед COM или EXE программой

в памяти. Так как адресация

начинается с шестнадцатеричного смещения 100 от начала PSP, то в

программе после оператора SEGMENT

кодируется директива ORG 100h.

28. Регистры микропроцессора. Регистры данных,

регистры указатели и сегментные регистры. Привести примеры.

Современные МП спроектированы таким образом,

что арифметические и логические инструкции и обращаются к памяти. Все

вышеуказанное выполняется с помощью программно адресных регистров которые можно

объединить в следующие группы:

1)регистры данных

2)регистры указатели

3)сегментные регистры

4)регистр флагов.

Регистры данных. Основное время при работе ЭВМ тратится на обращение к

памяти, при этом можно существенно повысить эффективность управляющих программ

сохраняя промежуточные результаты вычислений и операнды внутри МП. Для этого

служит четыре 16 разрядных арифметических регистра, эти регистры называются:

Пример 1: mov_CX,00; - инициализация CX

Пример 2: mov_DL,BH; -переносим

старший байт регистра ВХ в младший регистра DX.

Пример3: add_DX,AX; -сложение DX и AX, результат в DX.

AX – основной арифметический

регистр, называемый аккумулятором как правило только для арифметических и

логических операций.

ВХ – помимо использования в

арифметических операциях может использоваться для хранения смещения ячейки

памяти в режимах косвенной адресации, а также для хранения адреса начала

таблицы перекодировки символов.

СХ – помимо арифметических

операций, в этом регистре всегда хранится значение переменной цикла (счетчик

повторения).

DX – наряду

с арифметической операцией, этот регистр используется как расширение

аккумулятора для операций дающих 32 разрядный результат. Регистр DX всегда

используется для хранения адреса порта I/O в режимах косвенной адресации

периферийных устройств.

Регистры указатели. 5 регистров этой группы предназначены для точного

указания байта или слова в пространстве сегмента.

1)

IP Определяет

смещение следующей выполняемой инструкции в сегменте кода программы, т.е.

данный регистр следит за ходом выполнения программы. Программа не может явно

получить или изменить значение этого регистра, однако с помощью инструкций jmp

и call можно изменить значение IP, а также сохранить его значение в стеке с

последующим восстановлением.

2)

SP (Stek Pointer).

Этот регистр является 16 разрядным и он предназначен для работы со стеком.

Содержимое регистра SP указывает адрес элемента на вершине стека. Данная

информация необходима для организации процедур обслуживания прерываний, а также

при работе с циклами, с переменными и т.п. Как правило регистр SP не

используется в арифметических операциях.

3)

BP (Base Pointer (точка базы)). Данный 16

разрядный регистр применяется как дополнительный указатель для работы в

стековых структурах, в частности содержимое регистра BP позволяет обходить

параметры и промежуточные данные, записанные в стек. Регистр BP может в

большинстве арифметических и логических операциях. Одним из оснвных направлений

использования регистра BP является применение в режиме базово индексной

адресации памяти.

4)

SI (Search Index

(индекс источника )). Этот 16 разрядный регистр используется в арифметических и

логических операциях; в нем хранится адрес байта или слова строки в режимах

обработки строкового типа данных.

5)

DI (Destination Index (индекс приемника)). У

этого 16 разрядного регистра 2 функции: 1) арифметические и логические операции

и 2) хранит байт или слово приемника строки.

Сегментные регистры.

15 0

|

|

CS

15 0

|

|

DS

15 0

|

|

ES

15 0

|

|

SS

Процессоры до 80386 имеют

416-разрядных сигментных регистров CS,DS,ES,SS- начиная с

80386добавленно еще два 16-и разрядных регистра FS,GS.

15 0

|

|

FS

15 0

|

|

GS

Эти регистры называются

сегментными и обеспечивают адресацию 20-разрядного адресного пространства с

помощью 16-и разрядных операндов.

Регистр сегмента программы СS указывает на сегмент, который содержит текущую

последовательность выполняемых команд. Процессор выбирает команды из данного

сегмента, используя содержимое счетчика команд(EIP)как относительный адрес. Регистр не может быть

загружен явно.

Регистр сегмента стека SS указывает на сегмент в котором зарезервировано место

под стек. Все стековые команды

используют SS при обращении к стеку.

Регистры DS,ES, FS,GS являются

регистрами сегментов данных. Они содержат адреса сегментов, в которых находятся

данные программы.

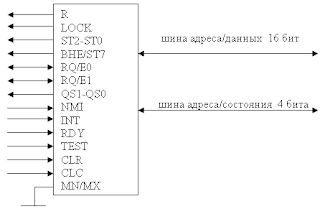

29. Сигнальные линии микропроцессора. Входные

сигнальные линии микропроцессора.

Взаимодействие МП с

окружающей средой заключается в выполнении одного из двух действий:

1.

МП либо выводит

(записывает) данные

2.

МП считывает

данные и команды.

Для реализации вышеуказанных

действий предназначены сигнальные линии МП.

Системную шину адреса/данных

образуют 20 сигнальных линий.

Линии AD15-AD0 –

мультиплексорная двунаправленная шина адреса/данных. По ее 16-ти линиям

передаются младшие 16 бит адреса памяти (или полный адрес порта I/O) и данные

А19/ST6-A16/ST3 –

шина адреса состояния, причем сигналы распределяются:

|

ST4

|

ST3

|

Сегментный регистр

|

|

0

0

1

1

|

0

1

0

1

|

ES

SS

CS

DS

|

На линиях ST4, ST3 определяется

сегментный регистр, участвующий в формировании 20-ти разрядного физического

адреса ячейки памяти.

Сигнальные линии

R (RD) – считывание, определяющее процедуру чтения из

памяти или порта ввода/вывода, то есть данный сигнал указывает этим устройствам

на необходимость выдачи данных на шину.

ST2-ST0

– сигналы состояния

|

ST2

|

ST1

|

ST0

|

Тип цикла шины

|

|

0

|

0

|

0

|

Подтверждает прерывания

|

|

0

|

0

|

1

|

Чтение из внешнего устройства

|

|

0

|

1

|

0

|

Запись во внешнее устройство

|

|

0

|

1

|

1

|

Остановка

|

|

1

|

0

|

0

|

Выборка команды

|

|

1

|

0

|

1

|

Чтение из ОЗУ

|

|

1

|

1

|

0

|

Запись в ОЗУ

|

|

1

|

1

|

1

|

Цикла шины нет

|

LOCK – блокировка шины

Активный сигнал информирует,

что доступ к шине должен быть заблокированным. Блокировка шины осуществляется

1-но байтовым префиксом “LOCK” в программе и поддерживается активным до

окончания следующей за префиксом команды.

BHE/ST7 – разрешение старшего байта состояния

Низкий уровень сигнала в начале цикла шины

означает, что байт данных передается по старшей

половине AD15-AD8 шины данных.

|

BHE

|

A0

|

Разрядность

данных

|

|

0

|

0

|

Word

|

|

0

|

1

|

Старший байт AD15-AD8

|

|

1

|

0

|

Младший байт AD7-AD0

|

|

1

|

1

|

НЕТ обращения

|

QS1-QS0 Состояние очереди команд

Значение этих

выходных сигналов определяет тип операции в очереди команд.

|

QS1

|

QS0

|

Операции над

очередью команд

|

|

0

|

0

|

Операций нет

|

|

0

|

1

|

Из очереди

выбран 1-й байт команд

|

|

1

|

0

|

Очередь пуста

после команда передачи управления

|

|

1

|

1

|

Из очереди

выбран следующий байт

|

30. Тест начальной загрузки BIOS POST.

По включению питания,

аппаратному сбросу от кнопки Reset или

нажатию клавиш:

«Ctrl-Alt-Delete» процессор переходит к исполнению начального

самотестирования, хранящегося в микросхеме BIOS

POST выполняет:

1)

тестирование

процессора

2)

тестирование

памяти

3)

тестирование

системных средств ввода-вывода

4)

конфигурирование

всех программно-управляемых средств системной платы

5)

инициализирует

загрузку ОС.

Во время выполнения POST выдаются диагностические сообщения в виде

последовательности коротких и длинных звуковых сигналов.

Последовательность шагов POST:

1)

Тестирование

регистров процессора

2)

Проверка

контрольной суммы ROMBIOS

3)

Проверка и

инициализация таймера i8253/8254 порт

8255

После этого шага доступная

звуковая диагностика

|

Сигнал

|

Ошибка

|

Возможные действия

|

|

1д 2к

|

Не обнаружен графический

адаптер

|

Установить/Переустановить

|

|

1д 3к

|

Не подключен монитор

|

Подключить монитор

|

|

1к

|

Ошибка регенерации DRAM

|

Желательно заменить RAM

|

|

2к

|

Ошибка паритета DRAM

|

Заменить память

|

|

3к

|

Ошибка в первых 64 Мб DRAM

|

Заменить DRAM

|

|

4к

|

Ошибка системного таймера

|

Ремонт системной платы

|

|

5к

|

Ошибка процессора

|

Заменить процессор

|

|

6к

|

Ошибка в контроллере

клавиатуры (KB)

|

Заменить клавиатуру

|

|

7к

|

Ошибка защищенного режима

|

Ремонт системной платы

|

|

8к

|

Ошибка видеопамяти

|

Заменить VRAM

|

|

9к

|

Ошибка контрольной суммы ROMBIOS

|

Заменить/перезаписать BIOS

|

|

10к

|

Ошибка CMOS

|

Ремонт системной платы

|

|

11к

|

Ошибка кэш-памяти

|

Заменить кэш-память

|

4)

Проверка и

инициализация контроллеров Прямого Доступа к Памяти (DMA) DMA 8237

5)

Загрузка векторов

прерывания из стека в нижнюю область памяти

6)

Инициализации

видеоконтроллера. На экране появляется VideoBIOS с указанием модели видеокарты и объемом установленной

памяти

После успеха этого шага

изображение на экране сменяется системной BIOS со счетчиком объема тестируемой DRAM. Начиная с этого момента все диагностические

сообщения выводятся на экран

|

Сообщение

|

Причины и возможные

действия

|

|

PRESS A KEY TO REBOOT

|

Нажать любую клавишу для

перезагрузки

|

|

SYSTEM HALTED, TO REBOOT

|

Остановка ПЭВМ при

обнаружении серьезной ошибки

|

|

CMOS

|

Упало напряжение на CMOS’e проверить

напряжение при выключенном питании, желательно >3В

|

|

CMOS CHECKSUM FAILURE

|

Ошибка контрольной суммы CMOS. Проблема с питанием и действие вируса

|

|

CMOS TIME & DATE NOT SET

|

Выполнить Setup и задать время и дату

|

|

KEYBOARD ERROR

K/B INTERFACE ERROR

NO KEYBOARD PRESENT

|

Ошибка в клавиатуре

|

|

DISK BOOT FAILURE

|

Нет доступного загрузочного

устройства

|

|

INVALID BOOT DISKETTE

|

Невозможно загрузить ОС с

дискеты

|

|

FDD CONTROLLER FAILURE

|

Ошибка контроллера

накопителей на FDD

|

|

HDD CONTROLLER FAILURE

|

Ошибка контроллера

накопителей на HDD

|

|

C:(D:) DRIVE ERROR

|

Невозможно обращение к

диску C или D

|

|

INTR#1 ERROR

|

Ошибка контроллера превываний,

отвечающего за линии IRQ 0..7

|

|

INTR#2 ERROR

|

Ошибка контроллера

превываний, отвечающего за линии IRQ

8..15

|

7)

Тестирование

полного объема ОЗУ

8)

Тестирование

клавиатуры

9)

Инициализация COM и LPT портов

10)

Вызов Boot Record

(Начальный загрузчик) прерывания Int 19h – Загрузчик ОС при неудаче; основ процессора с

сообщением (System Halted)

Комментариев нет:

Отправить комментарий